Potranno sembrare l’oggetto meno fashion che si possa immaginare, ma anche transistor e microchip sono vittime del marketing. Ogni volta che deve uscire un nuovo chip che alimenterà i PC e gli smartphone di prossima generazione, fra le aziende scatta la gara per chi sarà il primo a tagliare il traguardo dei 3 nm, dei 2 nm, e già si parla di 1 nm… Ma la verità è più complessa di così, e anche dietro a un innocente chip può nascondersi una bugia.

Perché la parola “nanometri” non significa più niente per transistor e semiconduttori

Era il 1971 quando nei laboratori Intel nasceva il primo microprocessore della storia, l’Intel 4004 fabbricato a 10 µm (10 micrometri). Questa fu l’unità di misura che venne mantenuta fino alla fine degli anni ‘80, quando dai micrometri si passò ai nm (nanometri). Ok, ma che cos’è un nanometro? E perché è così importante? Il nanometro è l’unità di misura del cosiddetto nodo tecnologico, e in principio indicava la dimensione di una componente del transistor, cioè la lunghezza del gate, elemento chiave in quanto controlla il passaggio di elettroni e sostanzialmente controlla accensione e spegnimento del transistor. Più il gate è piccolo più lo è il transistor, più il transistor è piccolo più ce ne stanno in un chip, più transistor ci sono più il chip è potente ma non solo, perché più transistor ci sono meno distanza devono percorrere gli elettroni, e questo significa più efficienza, meno consumi e temperature più basse.

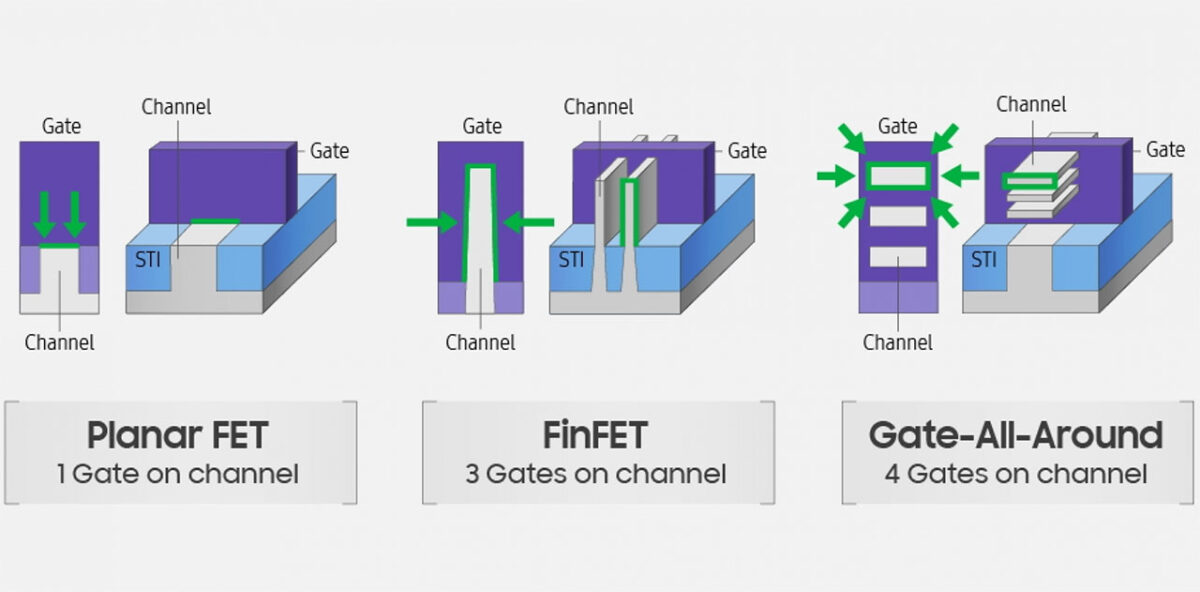

Su queste basi nacque la Legge di Moore, secondo cui il numero di transistor poteva raddoppiare con cadenza e dimensione prevedibile: ogni 1/2 anni, i nanometri potevano calare di circa 0,7 volte, passando quindi da 800 a 600 nm, da 600 a 350 nm, da 350 a 250 nm e così via. Con questo consapevolezza, l’industria dei semiconduttori sapeva che ogni tot mesi arrivava un preciso salto evolutivo; se i primi Pentium avevano 3,5 milioni di transistor, i Pentium 2 ne avevano 7 milioni. Nel 1997, però, qualcosa si inceppò. Con il passaggio da 350 a 250 nm Intel lanciò i Pentium 3, la cui potenza era sì raddoppiata, ma il gate non misurava 250 nm come previsto bensì 190 nm. Intel si accorse che poteva rimpicciolire sì il gate ma non le altre parti del transistor, perché la continua miniaturizzazione significava il rischio dell’effetto tunnel, quando il transistor è così piccolo che non riesce a trattenere gli elettroni con conseguenti malfunzionamenti; inoltre, i chip iniziavano a essere troppo piccoli per essere stampati efficientemente dalle macchine litografiche.

Fu così che si passò dai transistor planari ai FinFET, la cui struttura tridimensionale arginava questi limiti. Nel 2011, Intel lanciò i primi FinFET a 22 nm dove però nessuna parte del transistor misurava 22 nm; tuttavia, quell’unità di misura venne mantenuta per far capire che il chip fosse potente tanto quanto lo sarebbe stato un ipotetico chip realmente a 22 nm, facendo così perdere al nanometro il suo significato originale. E fin qua direte ok, ma qual è il problema? Vi ricordate la vicenda delle fotocamere da 1”? Ve l’ho spiegata in questo video-editoriale: in poche parole, le misure dei sensori fotografici non sono reali perché si rifanno a una misura del passato che è stata comunque mantenuta, e per evitare confusione tutti continuano a usarla in egual maniera, perciò se due smartphone hanno un sensore da 1”, anche se non sono veramente da 1”, le dimensioni sono uguali per entrambi. Il problema è che non è così che funziona nel mondo dei transistor, dove due chip con gli stessi nanometri non è detto che siano grandi uguali.

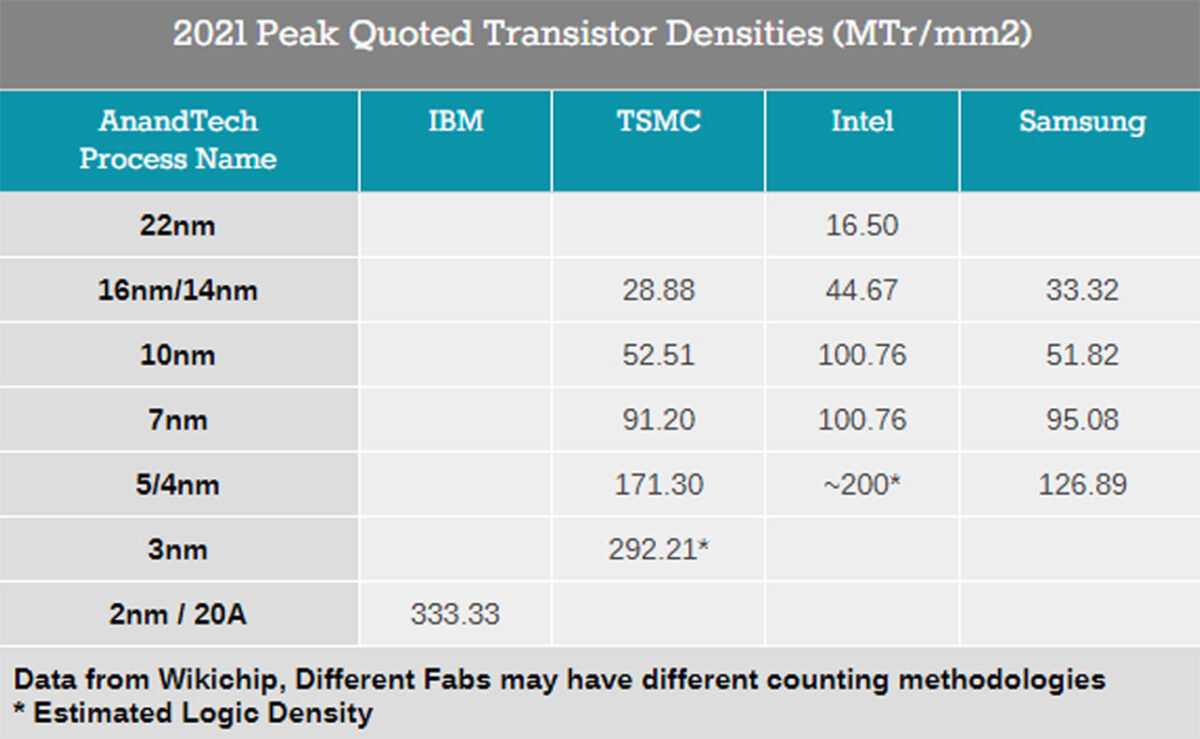

Che il nodo tecnologico diventi uno strumento di marketing ce ne si accorge quando si scopre che ci sono chip TSMC e Samsung a 10 nm che hanno la metà dei transistor dei chip Intel a 10 nm. Senza contare che TSMC e Samsung hanno più versioni degli stessi nodi: se si prendono tre chip a 5 nm com Snapdragon 888, A14 Bionic e Kirin 9000, quello di Qualcomm ha 10 miliardi di transistor, quello di Apple 12 miliardi e quello di Huawei oltre 15 miliardi.

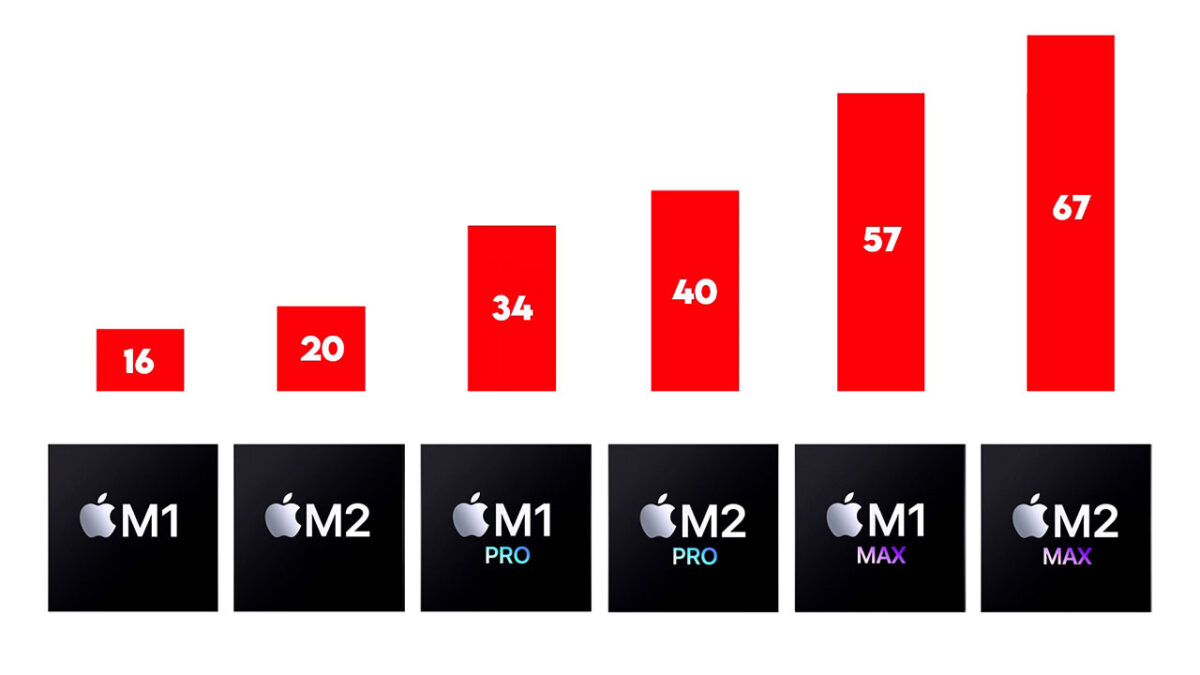

Oppure Apple M1 ed M2, sempre a 5 nm: la serie M1 arriva a 57 miliardi, mentre quella M2 fino a 67 miliardi.

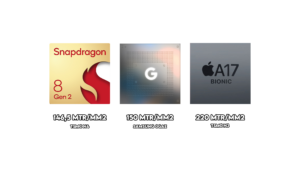

Vi faccio un altro esempio: dai 14 nm dello Snapdragon 820 ai 10 nm dell’835 il numero dei transistor è quasi raddoppiato, e lo stesso vale passando ai 7 nm dell’855. Tuttavia, dai 5 nm dell’888 ai 4 nm di 8 Gen 1 e Gen 2 il numero è quasi invariato; e la situazione non migliora granché col passaggio a 3 nm, con Google Pixel 3 che potrebbe anche prendersi il merito di essere il primo a 3 nm grazie al Tensor G3 di Samsung, un record che però lascerebbe il tempo che troverebbe quando iPhone 15 sempre a 3 nm avrà un numero ben superiore di transistor.

Questo report di Tech Insights dimostra come il Dimensity 9000 promosso da MediaTek come il primissimo a 4 nm sia essenzialmente uguale a quelli a 5 nm. Ancora più assurda è la vicenda di Samsung Galaxy S22 e le due versioni Snapdragon 8 Gen 1 ed Exynos 2200, entrambi fabbricati da Samsung: in origine, l’Exynos 2200 nasceva a 4 nm mentre lo Snapdragon 8 Gen 1 a 5 nm, ma Samsung non poteva certo fare uscire due versioni dello stesso telefono con chip apparentemente di generazioni diverse. Quello che fece fu “convertire” il processo produttivo dello Snapdragon a 4 nm, ma fisicamente era comunque rimasto come fosse a 5 nm. E la cosa ancora più paradossale è che l’S22 con Snapdragon a 5 nm dimostrò di funzionare meglio dell’S22 con Exynos a 4 nm: per la fretta di battere sul tempo TSMC, l’Exynos 2200 si rivelò un flop tale da convincere Qualcomm a tornare da TSMC e Samsung ad mettere in pausa il progetto Exynos.

Se una volta un chip a 350 nm era automaticamente migliore di uno a 600 nm, oggi non è detto che sia sempre così, perché il nanometro è diventata solo una stima, un’indicazione che i chipmaker usano per far capire che il nuovo chip è in qualche modo migliore del precedente, con tutte le ambiguità del caso. E non posso non pensare che la crisi dei semiconduttori abbia accentuato questa ambiguità, in un mondo dove i chip sono una valuta preziosissima e dove essere il primo a sbandierare un nuovo processo produttivo può rinsaldare la propria leadership, ma anche rivelarsi un’arma a doppio taglio.

Nel 2004, un wafer di chip a 90 nm costava 2.000$, mentre oggi un wafer a 3 nm costa 10 volte tanto, e pochissimi clienti possono permetterseli (principalmente Apple, Qualcomm, NVIDIA e MediaTek). Capirete da voi che TSMC e Samsung corrono sul filo del rasoio, perché hanno bisogno di questi clienti danarosi per ottenere i miliardi necessari per investire nei loro impianti, e per accaparrarsi questi clienti devono essere i primi a innovare, con il rischio o di anticipare troppo i tempi e fare come Samsung o di essere troppo cauti e farsi sorpassare. Ed è proprio questo cane che si morde la coda che porta le nuove tecnologie a essere usate solamente per metterci la bandierina sopra. Come al solito, quindi, l’invito è quello di essere consumatori consapevoli e non finire vittime del marketing.

⭐️ Scopri le migliori offerte online grazie al nostro canale Telegram esclusivo.