Da anni, i chipmaker del settore degli smartphone (Qualcomm e MediaTek) ci hanno abituato a una costante evoluzione dei System-on-a-Chip. Non soltanto sotto il profilo di CPU, GPU e memorie, ma anche sotto quello del processo produttivo. Per esempio, il 2022 è stato l’anno dei 4 nm, visti per la prima volta su SoC quali Snapdragon 8 Gen 1 e Dimensity 9000, preceduti nel 2020 dai 5 nm dello Snapdragon 888 Apple A14, e così via. Ma se negli anni passati la miniaturizzazione in nanometri avveniva in media ogni anno, adesso siamo giunti a un rimpicciolimento così avanzato e complesso da richiedere più tempo per poter essere eseguito.

TSMC sta preparando i suoi futuri chip a 3 e 2 nm, e i produttori tech ringraziano

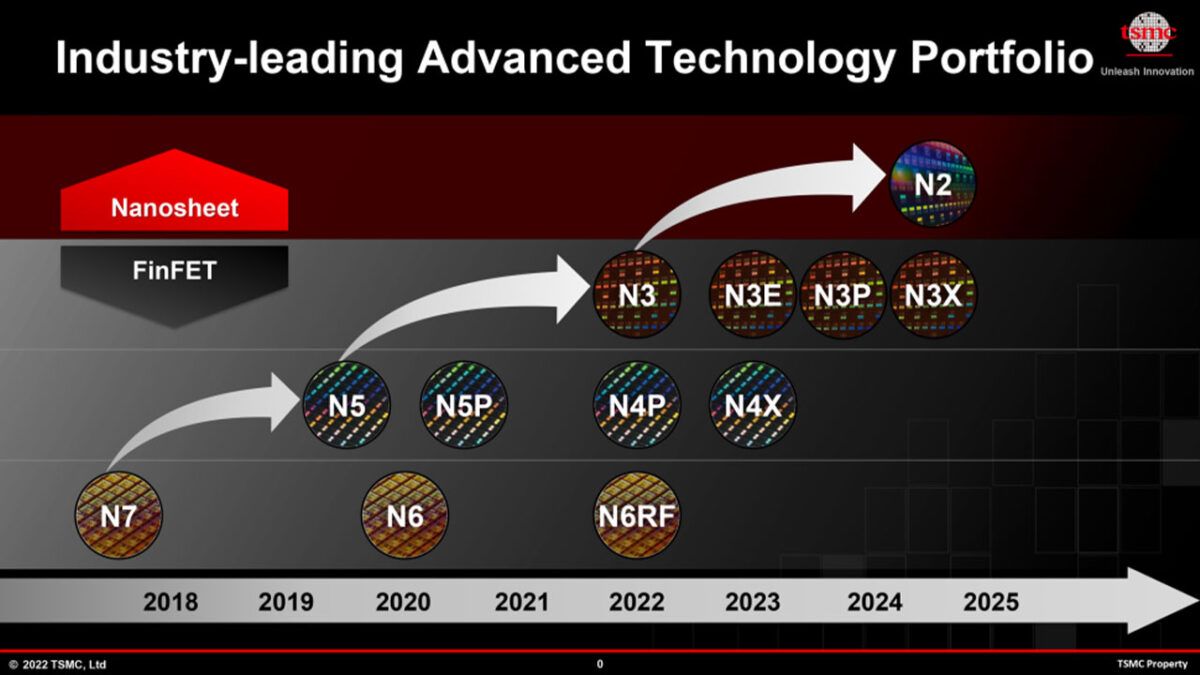

Lo si nota dalla cronologia di TSMC: 16 nm nel 2016, 10 nm nel 2017 e 7 nm nel 2018, seguiti dai 5 nm nel 2020 e infine 4 nm nel 2022. Di conseguenza, ci si aspetterebbe che i primi SoC a 3 nm di TSMC dovrebbero arrivare fra 2 anni, ma così non sarà. E a dirlo è la stessa TSMC, che in occasione della conferenza Technology Symposium ha confermato che debutteranno nella entro fine 2022.

Tuttavia, il futuro Snapdragon 8 Gen 2 dovrebbe rimanere sugli attuali 4 nm, così come Apple A16. Di conseguenza, è plausibile che i 3 nm si mostreranno concretamente sugli scaffali nel corso del 2023. Come mostrato nella propria roadmap, il processo produttivo a 3 nm di TSMC sarà composto da cinque fasi: N3, N3E (Enhanced), N3P (Performance Enhanced), N3S (Density Enhanced) e N3X (Ultra High Performance). Questo significa che i primi SoC a 3 nm non saranno uguali a quelli che verranno lanciati negli anni successivi.

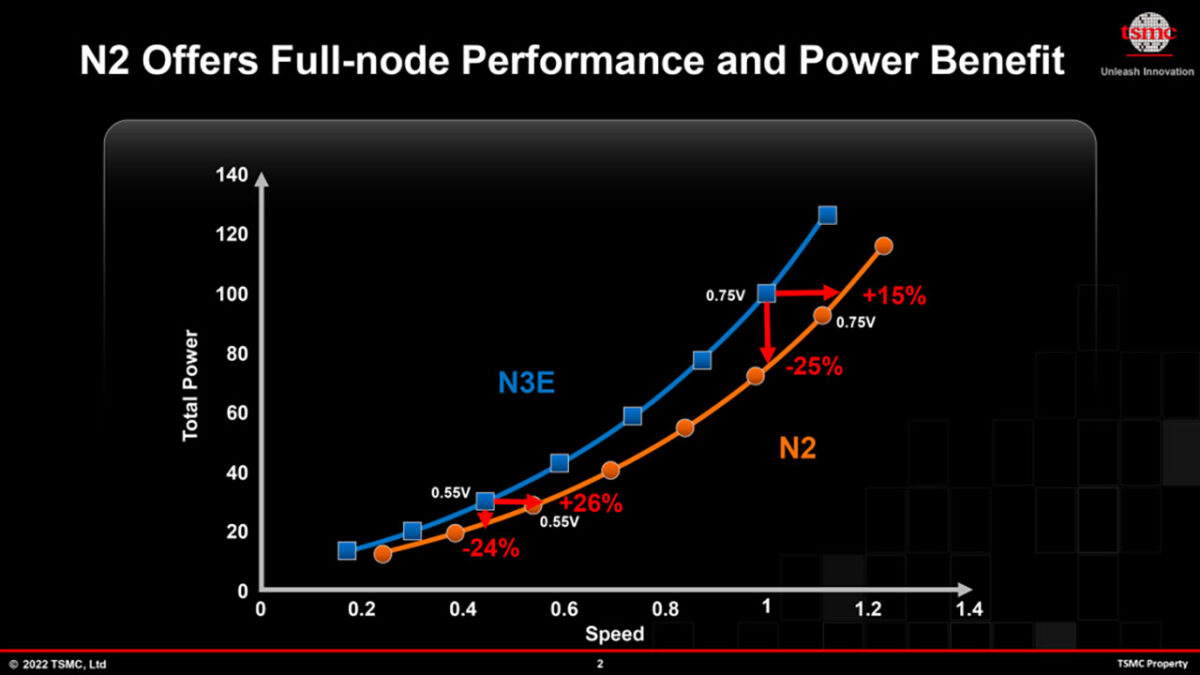

Ma la novità che in tanti attendono è fissata al 2025, anno di debutto per i primi SoC a 2 nm di fattura TSMC. Non solo per il salto in avanti in fatto di nanometri, ma anche perché dalla tecnologia FinFET si passerà a quella GAAFET (Gate-all-around FET). Tramite l’utilizzo di nuovi nanomateriali, permetterà ai SoC di godere di maggiore potenza a pari dimensione, potendo così ospitare più transistor. I primi dati a disposizione parlano di un salto in avanti rispetto a N3E del +10/15% di potenza e un abbassamento dei consumi del -25/30%. Lo sviluppo di una tecnologia come quella GAAFET è importante, perché è uno dei modi con cui TSMC (ma anche Samsung) vogliono ovviare ai limiti della legge di Moore, cioè al raggiungimento di un limite fisico per l’evoluzione dei microchip.

⭐️ Scopri le migliori offerte online grazie al nostro canale Telegram esclusivo.