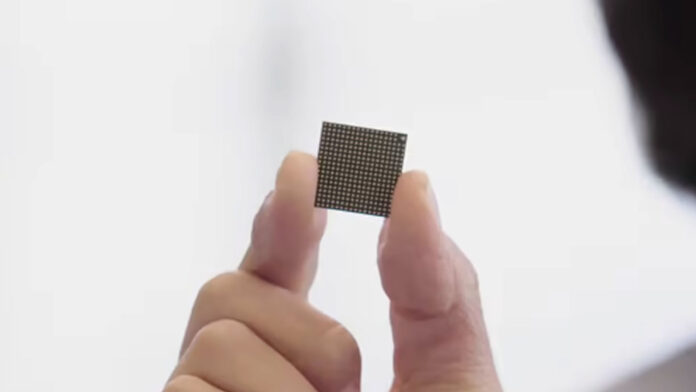

In occasione della conferenza IEDM tenutasi a San Francisco, Samsung e IBM hanno annunciato una grossa novità che riguarda il futuro dei chip a 1 nm. Quando si parla di realizzazione dei semiconduttori, parlare di “nanometri” significa fare riferimento al loro processo produttivo. Sin dalla loro creazione, i chipmaker hanno messo in atto tecnologie sempre più raffinate e avanzate per ridurre le dimensioni dei transistor. Questo perché più un transistor è piccolo, più è piccolo lo spazio che gli elettroni che scorrono al loro interno devono attraversare. Ciò significa sia un aumento delle prestazioni, potendone effettuare di più in minor tempo, sia un miglioramento dell’efficienza e della gestione delle temperature.

Se si volesse stilare una cronistoria in tal senso, si potrebbe partire dai chip PMOS/NMOS a 20.000 nm del 1960 arrivando agli attuali chip a 4 nm di TSMC e Samsung nel 2021. Ma cosa sono esattamente questi “nanometri”? Fino a qualche anno fa, erano l’unità di misura che indicava la lunghezza del gate, cioè quel pezzo del transistor che controlla il flusso degli elettroni. Riducendone la lunghezza (in nm) su un piano bidimensionale, si potevano così rimpicciolire i transistor e ottenere chip più piccoli ma più potenti. Con l’avvento dei chip FinFET negli anni 2000, i transistor hanno assunto forme più tridimensionali, permettendo ai chip di essere ulteriormente ridotti.